# AQA Computer Science A-Level 4.7.3 Structure and role of the processor and its components

**Past Paper Questions**

# Additional Specimen AS Paper 2

| There are many system design issues that affect processor performance and the use of multiple cores and cache memory are two of these.                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name and explain <b>two</b> more system hardware decisions that will effect processor performance and describe all <b>four</b> effects. Use examples to illustrate your description. |

| [6 marks]                                                                                                                                                                            |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

| ·                                                                                                                                                                                    |

| -                                                                                                                                                                                    |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

| <u></u>                                                                                                                                                                              |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

|                                                                                                                                                                                      |

### Additional Specimen Paper 2

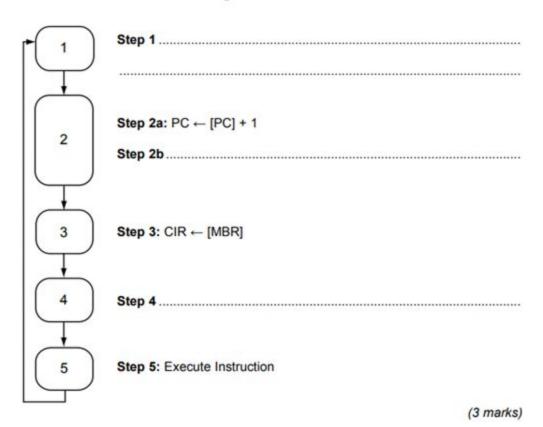

Figure 2 shows the fetch-execute cycle, excluding how interrupts are dealt with. Some of the steps in the cycle have been described.

Describe the missing steps 1, 2b and 4 using either register transfer notation or a written description. Steps 2a and 2b occur at the same time.

[3 marks]

Figure 2 Step 1 Step 2a PC ← [PC] + 1 (Increment contents of Program Counter Register) 2 Step 2b Step 3: CIR ← [MBR] 3 (Transfer contents of Memory Buffer Register into Current Instruction Register) Step 4

Step 5 Execute Instruction

| 0 4 . | 4      | An interrupt can occur during the fetch-execute cycle.                                                                                                                                           |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |        | Explain what happens when an interrupt occurs.  [4 marks]                                                                                                                                        |

|       |        |                                                                                                                                                                                                  |

|       |        | ·                                                                                                                                                                                                |

|       |        |                                                                                                                                                                                                  |

|       |        |                                                                                                                                                                                                  |

|       |        |                                                                                                                                                                                                  |

|       |        |                                                                                                                                                                                                  |

|       |        |                                                                                                                                                                                                  |

|       |        | January 2009 Comp 2                                                                                                                                                                              |

| 3 (a) | The    | high-level language statement                                                                                                                                                                    |

|       |        | A := B + 5                                                                                                                                                                                       |

|       | is to  | be written in assembly language.                                                                                                                                                                 |

|       | of the | nplete the following assembly language statements, which are to be the equivalent ne above high level language statement. The Load and Store instructions imply use of the accumulator register. |

|       |        | Load                                                                                                                                                                                             |

|       |        | #5                                                                                                                                                                                               |

|       |        | Store (3 marks)                                                                                                                                                                                  |

| 5 | The Fetch-Execute cycle can be described in register-transfer language as follows:                   |

|---|------------------------------------------------------------------------------------------------------|

|   | MAR ← [PC] PC ← [PC] + 1; MBR ← [Memory] <sub>addressed</sub> CIR ← [MBR] [CIR] decoded and executed |

|   | where [] means contents of.                                                                          |

|   | Describe the Fetch-Execute cycle in your own words.                                                  |

|   |                                                                                                      |

|   |                                                                                                      |

|   |                                                                                                      |

|   |                                                                                                      |

|   |                                                                                                      |

|   |                                                                                                      |

|   |                                                                                                      |

|   |                                                                                                      |

|   | (6 marks)                                                                                            |

|   |                                                                                                      |

|   |                                                                                                      |

## January 2010 Comp 2

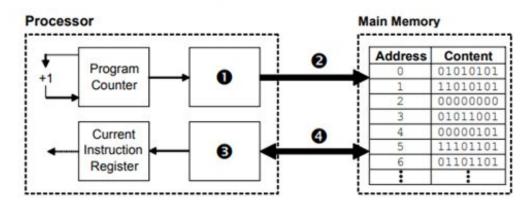

3 Figure 1 shows the fetch-execute cycle. Steps 2a and 2b occur at the same time.

| 3 | (a) | State the full names of <b>two</b> of the special purpose registers that are used in the fetch part of the fetch-execute cycle. |

|---|-----|---------------------------------------------------------------------------------------------------------------------------------|

|   |     | Register 1:                                                                                                                     |

|   |     | Register 2: (2 marks                                                                                                            |

| 3 | (b) | Explain the role of the address bus, data bus and main memory during Steps 1 and 2b.                                            |

|   |     |                                                                                                                                 |

|   |     |                                                                                                                                 |

|   |     |                                                                                                                                 |

|   |     |                                                                                                                                 |

|   |     | (2 marks                                                                                                                        |

| 3 | (c) | Give one reason why Steps 2a and 2b are able to occur at the same time.                                                         |

|   |     |                                                                                                                                 |

|   |     | (1 mark                                                                                                                         |

| 5 | A si | ngle a         | accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | microproc   | essor suppo   | orts the assembly language instructions:                                                           |

|---|------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------|----------------------------------------------------------------------------------------------------|

|   |      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | LOAD        | memory        | reference                                                                                          |

|   |      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ADD         | memory        | reference                                                                                          |

|   |      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | STORE       |               | reference                                                                                          |

|   | An   | examp          | ple instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | on is:      |               |                                                                                                    |

|   |      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |               | LOAD 4                                                                                             |

|   |      | ch wo<br>ster. | ould copy the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | contents    | of the refere | enced memory location 4 into the accumulator                                                       |

| 5 | (a)  | (i)            | The second secon |             |               | ction is the <i>operand</i> and which part is the <i>opcode</i> and opcode in the two boxes below. |

| 5 | (a)  | (ii)           | The accum                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             | general pur   | LOAD 4  (1 mark)  rpose register.                                                                  |

| 5 | (b)  | Hein           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | anguage in    | (1 mark) structions, write an assembly language program                                            |

| 3 | (0)  | that a         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r the value | es stored in  | memory locations 12 and 13, storing the                                                            |

|   |      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |               |                                                                                                    |

|   |      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |               |                                                                                                    |

|   |      |                | •••••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •••••       |               |                                                                                                    |

|   |      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             | •••••         |                                                                                                    |

|   |      |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •••••       |               | (3 marks)                                                                                          |

# January 2011 Comp 2

| 4 | Some of the assembly | language instructions supported by a simple microprocessor are |

|---|----------------------|----------------------------------------------------------------|

| - | Come of the accembly | language mondono supported by a simple misroprocessor are      |

| Assembly Language |

|-------------------|

| STORE             |

| LOAD              |

| ADD               |

Examples of the use of these assembly language instructions are:

| STORE | 5 | Copy the contents of the accumulator into memory location 5                                                             |

|-------|---|-------------------------------------------------------------------------------------------------------------------------|

| LOAD  | 5 | Copy the contents of memory location 5 into the accumulator                                                             |

| ADD   | 2 | Add the contents of memory location 2 to the current contents of the accumulator, storing the result in the accumulator |

4 (a) Write into the table below the opcode and the operand parts of the following instruction.

LOAD 5

| Operand |  |

|---------|--|

| Opcode  |  |

(1 mark)

| Write an assembly language program, using the instructions given above, that adds the contents of memory locations 7, 8 and 3, storing the answer in memory location 21. | (b) | 4 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|

|                                                                                                                                                                          |     |   |

|                                                                                                                                                                          |     |   |

|                                                                                                                                                                          |     |   |

|                                                                                                                                                                          |     |   |

|                                                                                                                                                                          |     |   |

|                                                                                                                                                                          |     |   |

| /2 morks                                                                                                                                                                 |     |   |

|                                                                                                                                                                          |     |   |

| 7     | A programmer could use either an assembly language or a high level language to code programs for sale. |

|-------|--------------------------------------------------------------------------------------------------------|

| 7 (a) | Give two limitations of using assembly language to code a program.                                     |

|       | 1                                                                                                      |

|       |                                                                                                        |

|       | 2                                                                                                      |

|       | (2 marks                                                                                               |

## January 2012 Comp 2

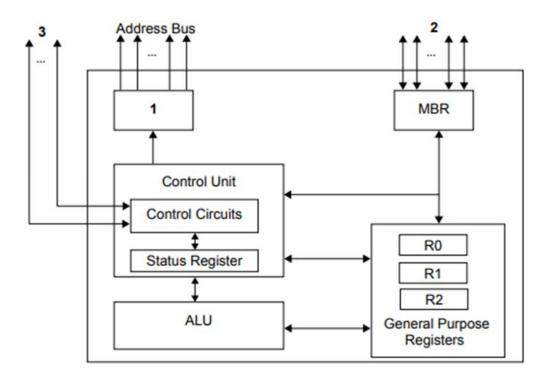

3 Figure 4 below shows an incomplete diagram of the components of a processor.

Figure 4

3 (a) Provide the full names for the components numbered 1 to 3 in Figure 4 by completing Table 1 below.

Table 1

| Component<br>Number | Component Name |

|---------------------|----------------|

| 1                   |                |

| 2                   |                |

| 3                   |                |

(3 marks)

| 3 (b) | What is the role of the Control Unit?                                                             |          |

|-------|---------------------------------------------------------------------------------------------------|----------|

|       |                                                                                                   |          |

|       |                                                                                                   | (1 mark) |

| 3 (c) | State the full name of the processor component that would perform subtract comparison operations. | ion and  |

|       |                                                                                                   |          |

|       |                                                                                                   | (1 mark) |

| 3 (d) | What is meant by the term register?                                                               |          |

|       |                                                                                                   |          |

|       |                                                                                                   | (1 mark) |

| 3 (e) | State one example of when the status register might have a bit set.                               |          |

|       |                                                                                                   |          |

|       |                                                                                                   | (1 mark) |

## June 2010 Comp 2

Figure 2 shows the processor registers and busses that are used during the fetch part of the fetch-execute cycle, together with the main memory. The values stored in memory locations 0 to 6 in the main memory are machine code instructions.

Figure 2

7 (a) Name the components that are labelled with the numbers 0 to 0. In the case of register names, the full names must be stated.

| Number | Component Name |

|--------|----------------|

| 0      |                |

| 0      |                |

| €      |                |

| 9      |                |

(4 marks)

| 7 | (b) | Explain what happens during the decode and execute stages of the fetch-execute cycle. |

|---|-----|---------------------------------------------------------------------------------------|

|   |     |                                                                                       |

|   |     |                                                                                       |

|   |     |                                                                                       |

|   |     |                                                                                       |

|   |     |                                                                                       |

|   |     | (3 marks)                                                                             |

# <u>June 2011 Comp 2</u>

Figure 2 and Figure 3 show different versions of the same program.

|     | Figure | 2   | Figure 3 |          |          |  |  |  |

|-----|--------|-----|----------|----------|----------|--|--|--|

| (x) | (y)    | (z) | (x)      | (y)      | (z)      |  |  |  |

| 200 | LOAD   | 7   | 200      | 01010110 | 00000111 |  |  |  |

| 201 | ADD    | 3   | 201      | 11010000 | 00000011 |  |  |  |

| 202 | ADD    | 6   | 202      | 11010000 | 00000110 |  |  |  |

| 203 | STORE  | 255 | 203      | 11110000 | 11111111 |  |  |  |

| 4 | (a) | What generation of programming language is shown in Figure 2?               |           |

|---|-----|-----------------------------------------------------------------------------|-----------|

|   |     |                                                                             | (1 mark)  |

| 4 | (b) | In both figures there is a column labelled (x).                             |           |

|   |     | What would be a suitable heading for this column?                           |           |

|   |     |                                                                             | (1 mark)  |

| 4 | (c) | In both figures the instruction is split into two parts.                    |           |

|   |     | What are the names of the instruction parts in columns (y) and (z)?         |           |

|   |     | ( <b>y</b> )                                                                |           |

|   |     | (z)                                                                         | (2 marks) |

| 4 | (d) | What is the relationship between the instructions in Figure 2 and Figure 3? |           |

|   |     |                                                                             |           |

|   |     |                                                                             | (1 mark)  |

| 7         | (b) | In the first step of the Fetch-Execute Cycle the contents of the Program Counter are copied into another register. |

|-----------|-----|--------------------------------------------------------------------------------------------------------------------|

|           |     | State the <b>full name</b> of this register.                                                                       |

|           |     | (1 mark)                                                                                                           |

| 7 (c)     |     | An item of data or an instruction fetched into the processor is initially loaded into a register.                  |

|           |     | State the <b>full name</b> of this register.                                                                       |

|           |     | (1 mark)                                                                                                           |

|           |     | June 2012 Comp 2                                                                                                   |

| 2         | (a) | A machine code instruction can be split into an opcode part and an operand part.                                   |

| 2 (a) (i) |     | What does an opcode represent?                                                                                     |

|           |     |                                                                                                                    |

|           |     | (1 mark)                                                                                                           |

| 2 (a) (ii |     | What does an operand represent?                                                                                    |

|           |     |                                                                                                                    |

|           |     | (1 mark)                                                                                                           |

|           |     |                                                                                                                    |

- 5 The following registers are used in the Fetch-Execute cycle:

- Current Instruction Register (CIR)

- Memory Address Register (MAR)

- Memory Buffer Register (MBR)

- Program Counter (PC)

- Status Register (SR)

Describe, using full sentences, the steps involved in the Fetch-Execute cycle, making reference to how the registers above are used. Your description should cover the fetch, decode and execute phases of the cycle. You may use the abbreviations given above for the register names in your response; for example PC for Program Counter.

| organise your answer clearly in complete sentences, using specialist vocabulary where appropriate. |

|----------------------------------------------------------------------------------------------------|

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

|                                                                                                    |

| (6 marks                                                                                           |

## June 2013 Comp 2

| 2 (a) | State the full names of two of the special purpose registers that are used in the fetch |

|-------|-----------------------------------------------------------------------------------------|

|       | part of the fetch-execute cycle.                                                        |

2 (b) Figure 1 below is an incomplete diagram of the fetch-execute cycle.

Describe the missing steps 1, 2b and 4 using either register transfer notation or a written description. Steps 2a and 2b occur at the same time.

Figure 1

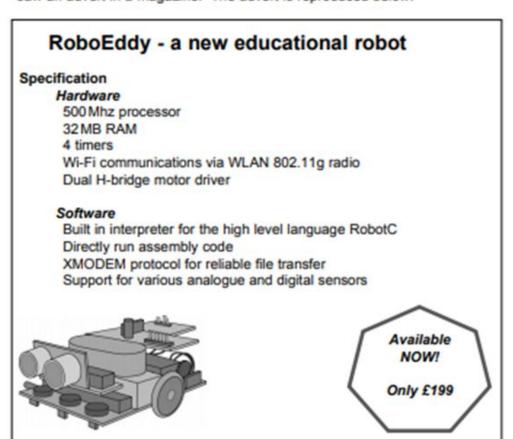

A school robotics club has recently purchased a robotics kit after the teacher in charge saw an advert in a magazine. The advert is reproduced below.

| 4 (d) | As well language                                                                                                                                                                                 |                                                                                   | ng RobotC, it is also possible to program the robot using assembly |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|--|--|--|

|       | The motor driver uses memory locations to store the current speed of each motor. The left motor speed is stored in memory location 21 and the right motor speed is stored in memory location 22. |                                                                                   |                                                                    |  |  |  |  |  |  |

|       | The following set of three assembly language instructions can be used to take basic control of the motors:                                                                                       |                                                                                   |                                                                    |  |  |  |  |  |  |

|       | LOAD                                                                                                                                                                                             | XX                                                                                | - load a value from memory location XX into the accumulator        |  |  |  |  |  |  |

|       | ADD                                                                                                                                                                                              | <ul> <li>add the value stored in memory location XX to the accumulator</li> </ul> |                                                                    |  |  |  |  |  |  |

|       | STORE                                                                                                                                                                                            | XX                                                                                | - store the value in the accumulator in memory location XX         |  |  |  |  |  |  |

|       | Selecting from the set of three instructions above, write a sequence of instructions that will swap the current left motor speed with the current right motor speed. Your program                |                                                                                   |                                                                    |  |  |  |  |  |  |

|       | may use memory location 23 for temporary storage.                                                                                                                                                |                                                                                   |                                                                    |  |  |  |  |  |  |

|       |                                                                                                                                                                                                  |                                                                                   |                                                                    |  |  |  |  |  |  |

|       |                                                                                                                                                                                                  |                                                                                   |                                                                    |  |  |  |  |  |  |

|       | ************                                                                                                                                                                                     |                                                                                   |                                                                    |  |  |  |  |  |  |

|       |                                                                                                                                                                                                  |                                                                                   |                                                                    |  |  |  |  |  |  |

|       | •••••                                                                                                                                                                                            |                                                                                   |                                                                    |  |  |  |  |  |  |

|       |                                                                                                                                                                                                  |                                                                                   | (3 marks)                                                          |  |  |  |  |  |  |

June 2016 AS Paper 2

Table 2 - standard AQA assembly language instruction set

| LDR Rd, <memory ref=""></memory>          | Load the value stored in the memory location specified by<br><memory ref=""> into register d.</memory>                                                                                                                                                   |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STR Rd, <memory ref=""></memory>          | Store the value that is in register d into the memory location<br>specified by <memory ref="">.</memory>                                                                                                                                                 |

| ADD Rd, Rn, <operand2></operand2>         | Add the value specified in <operand2> to the value in<br/>register n and store the result in register d.</operand2>                                                                                                                                      |

| SUB Rd, Rn, <operand2></operand2>         | Subtract the value specified by <pre><operand2> from the value in register n and store the result in register d.</operand2></pre>                                                                                                                        |

| MOV Rd, <operand2></operand2>             | Copy the value specified by <pre><pre>coperand2&gt; into register d.</pre></pre>                                                                                                                                                                         |

| CMP Rn, <operand2></operand2>             | Compare the value stored in register n with the value<br>specified by <pre><pre>coperand2&gt;</pre>.</pre>                                                                                                                                               |

| B <label></label>                         | Always branch to the instruction at position <1abel> in the program.                                                                                                                                                                                     |

| B <condition> <label></label></condition> | Branch to the instruction at position <label> if the last comparison met the criterion specified by <condition>. Possible values for <condition> and their meanings are:  EQ: equal to  OCT: greater than  LT: less than</condition></condition></label> |

| AND Rd, Rn, <operand2></operand2>         | Perform a bitwise logical AND operation between the value<br>in register n and the value specified by <perand2> and<br/>store the result in register d.</perand2>                                                                                        |

| ORR Rd, Rn, <operand2></operand2>         | Perform a bitwise logical OR operation between the value in<br>register n and the value specified by <pre><operand2></operand2></pre> and<br>store the result in register d.                                                                             |

| EOR Rd, Rn, <operand2></operand2>         | Perform a bitwise logical XOR (exclusive or) operation<br>between the value in register n and the value specified by<br><perand2> and store the result in register d.</perand2>                                                                          |

| MVN Rd, <operand2></operand2>             | Perform a bitwise logical NOT operation on the value<br>specified by <pre><operand2></operand2></pre> and store the result in register d.                                                                                                                |

| LSL Rd, Rn, <operand2></operand2>         | Logically shift left the value stored in register n by the<br>number of bits specified by <pre><operand2></operand2></pre> and store the<br>result in register d.                                                                                        |

| LSR Rd, Rn, <operand2></operand2>         | Logically shift right the value stored in register n by the<br>number of bits specified by <pre><pre>cperand2&gt;</pre> and store the<br/>result in register d.</pre>                                                                                    |

| HALT                                      | Stops the execution of the program.                                                                                                                                                                                                                      |

Labels: A label is placed in the code by writing an identifier followed by a colon (:). To refer to a label, the identifier of the label is placed after the branch instruction.

#### Interpretation of <operand2>

<operand2> can be interpreted in two different ways, depending on whether the first

character is a # or an R:

- # Use the decimal value specified after the #, eg #25 means use the decimal value 25.

- Rm Use the value stored in register m, eg R6 means use the value stored in register 6.

The available general purpose registers that the programmer can use are numbered 0 to 12.

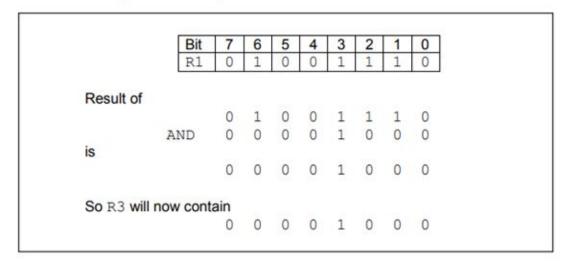

The AND instruction can be used to help identify if a particular bit in a register contains a 1. The instruction AND R3, R1, #8 will perform the logical bitwise AND operation between the contents of register R1 and the bit pattern 0000 1000 and store the result in register R3. If register R1 has a 1 in bit 3 then the bit pattern for the decimal number 8 will be stored in register R3, otherwise the bit pattern for the decimal number 0 will be stored in register R3.

Figure 2 and Figure 3 show examples of this.

Figure 2 – Example when bit 3 of R1 contains a 1

Figure 3 – Example when bit 3 of R1 contains a 0

|               | Bit      | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---------------|----------|-----|---|---|---|---|---|---|---|

|               | R1       | 0   | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

| Result of     |          |     |   |   |   |   |   |   |   |

|               |          | 0   | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

|               | AND      | 0   | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| is            |          |     |   |   |   |   |   |   |   |

|               |          | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| So R3 will n  | our cont | oin |   |   |   |   |   |   |   |

| SO K3 WIII II | ow cont  |     | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|               |          | U   | 0 | 0 | U | U | U | 0 | 0 |

**0 4** . **2** All even numbers are represented by bit patterns ending with a 0; all odd numbers are represented by bit patterns ending with a 1.

Complete the assembly language instruction below to help identify if register R1 contains an odd number, storing the result of this operation in register R3.

[1 mark]

AND R3, R1,

| 04.3 | <b>Figure 4</b> shows a block of code, written in a high-level language, that is used to find out if the number stored in the variable $\mathbb A$ is even. If the value is even then the number $69_{10}$ is stored in the variable $\mathbb B$ , otherwise the number $79_{10}$ is stored in the variable $\mathbb B$ . |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Figure 4                                                                                                                                                                                                                                                                                                                  |

|      | IF IsEven(A)  THEN B 		69  ELSE B 		79  ENDIF                                                                                                                                                                                                                                                                             |

|      | Write a sequence of assembly language instructions that would perform the same operations as the high-level language code in <b>Figure 4</b> .                                                                                                                                                                            |

|      | Assume that register $R1$ currently stores the value associated with $A$ , that register $R2$ stores the value currently associated with $B$ and that register $R3$ is available for general use, if necessary.                                                                                                           |

|      | Your answer to question 0 4 . 2 can be reused as part of your answer to this question. [6 marks]                                                                                                                                                                                                                          |

|      |                                                                                                                                                                                                                                                                                                                           |

|      |                                                                                                                                                                                                                                                                                                                           |

|      |                                                                                                                                                                                                                                                                                                                           |

| 04.4 | Shade in <b>one</b> lozenge to indicate which addressing mode is being used with the second operand in the assembly language instruction MOV R2, #0.  [1 mark]  Direct   Immediate                                                                                                                                        |

| 0 4 . 5 | Explain what a register is. | [1 mark] |

|---------|-----------------------------|----------|

|         | <del>.</del>                |          |

|         |                             | -        |

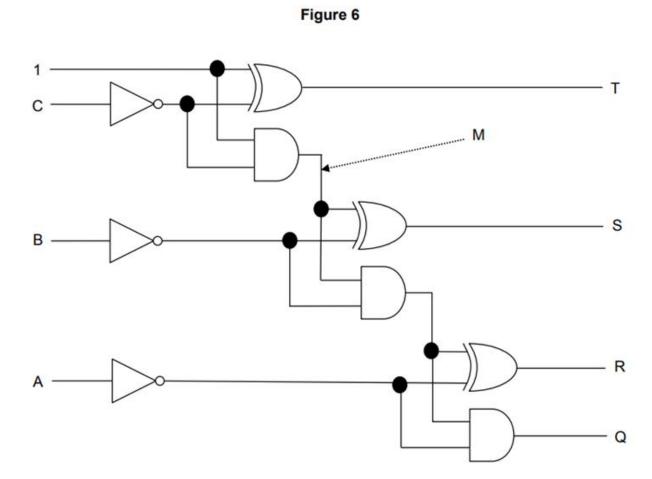

Figure 6 shows a logic circuit that might be found inside a processor.

| 0 5 . 6 | The circuit in <b>Figure 6</b> can be simplified so that it uses fewer logic gates but still has the same functionality. Changing the design of the circuits used in a processor can improve processor performance. Increasing the number of cores can also improve processor performance. |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|