# AQA Computer Science A-Level 4.7.1 Internal hardware components of a computer

Past Paper Mark Schemes

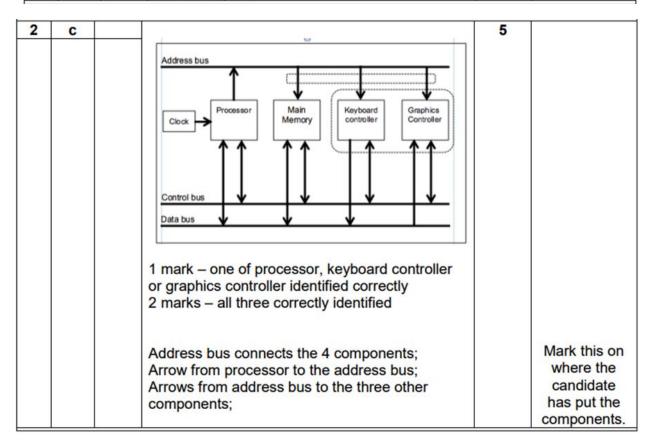

#### Additional Specimen Paper 2

| 04 | 1 | Mark is for AO1 (understanding) | 4 |

|----|---|---------------------------------|---|

|    |   | Architecture A;                 | 1 |

#### 1 mark for AO1 (recall): Situation (MAX 1 mark): 04 3 Digital signal processing; Microprocessors / embedded devices / microcontrollers; A. Internal processor structure for caching A. other reasonable examples 2 marks for AO1 (understanding): Advantages (MAX 2 marks): Instruction and data can be accessed simultaneously; Avoid/reduce bottleneck of single data/address bus(es) // avoid/reduce delays waiting for memory fetches; Instruction and data memory can have different word lengths; Different technologies can be used to implement instruction and data memory; Different quantities of instruction and data memory means that address lengths can differ between the two // memory address structures can differ; Avoids possibility of data being executed as code, which is one method that can be exploited by hackers;

#### January 2010 Comp 2

| 3 | (a)   | Program Counter; A Sequence Control Register R Next Instruction |   |

|---|-------|-----------------------------------------------------------------|---|

|   | 1.4.0 | Register                                                        |   |

|   |       | Current Instruction Register; A Instruction Register            |   |

|   |       | Memory Buffer Register; A Memory Data Register                  |   |

|   |       | Memory Address Register;                                        |   |

|   |       | MAX 2                                                           | 2 |

|   |       | Supples and the second second                                   |   |

| 3 | (b) | Address in MAR/address to fetch instruction from, sent down Address Bus to Main Memory; R address in PC (program counter) Contents of address accessed in Main Memory; A by implication if contents of address location referred to during data transfer Contents of address location//instruction//data passed down Data Bus into MBR/to processor; A MDR instead of MBR A RAM for Main Memory MAX 2 | 2 |

|---|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| 3 | (c) | Order of execution unimportant/one step does not rely on prior completion of the other; Steps carried out by different (hardware) devices/components; A operations are independent A operations use different registers R using different buses MAX 1                                                                                                                                                 | 1 |

## January 2011 Comp 2

| 1 | а | Address (bus);                                                                       | 1 |  |

|---|---|--------------------------------------------------------------------------------------|---|--|

| 1 | b | 1; <b>R</b> 33                                                                       | 1 |  |

| 1 | С | A – Visual display unit; A VDU B – Processor; R CPU C – (Main) memory; D – Keyboard; | 4 |  |

## January 2013 Comp 2

| 2 | a | A set of/group of/parallel wires/lines;                                                                   | MAX | Wires needs                          |

|---|---|-----------------------------------------------------------------------------------------------------------|-----|--------------------------------------|

|   |   | that are used to connect together components (inside the computer) // connect different parts of the CPU; | 2   | to be<br>qualified with<br>set/group |

|   |   | in order to pass signals between them;                                                                    |     |                                      |

|   |   | R a wire A. connect different parts of the computer NE data                                               |     |                                      |

| A. Commands / machine-code R signals          | e                                                                                                                                                |                                                               |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| _                                             |                                                                                                                                                  |                                                               |

| Examples of a control signa                   | ıl (max 1):                                                                                                                                      | NE an event                                                   |

| request; bus grant; bus reques                | st; status; I/O write;                                                                                                                           | that details<br>when an<br>interrupt<br>would be<br>caused    |

| A. interrupt A. transfer reques A. read/write | t                                                                                                                                                |                                                               |

| NE load /store                                |                                                                                                                                                  |                                                               |

|                                               | Clock/timing; reset; interrupt A request; bus grant; bus request/O read; memory read; memory ACK  A. interrupt A. transfer request A. read/write | A. interrupt A. transfer request A. read/write NE load /store |

## <u>June 2011 Comp 2</u>

| 7 | а | 1 – clock; 2 – (Main) memory / IAS;                                                                                             | 5 |

|---|---|---------------------------------------------------------------------------------------------------------------------------------|---|

| 7 | d | Address bus has 64 lines / tracks/ wires // there are 2 ^64 memory locations available;  NE 64 bits wide, moves 64 bits of data | 1 |

## June 2017 AS Paper 2

| 1 | Marks are for AO1 (understanding)                                                                                                        | 2                                                                                                                                                                                                                                                                                                                                                         |

|---|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Harvard uses separate memory/bus/address space // von Neumann uses combined memory/bus/address space; for instructions/program and data; |                                                                                                                                                                                                                                                                                                                                                           |

|   | NE. Places, locations, registers, areas of memory                                                                                        |                                                                                                                                                                                                                                                                                                                                                           |

|   | A. Main memory                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                           |

|   |                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                           |

|   | separately in memory.                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                           |

| 2 | Mark is for AO1 (knowledge)                                                                                                              | 1                                                                                                                                                                                                                                                                                                                                                         |

|   | Harvard;                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                           |

|   | R. more than one lozenge shaded                                                                                                          |                                                                                                                                                                                                                                                                                                                                                           |

|   | 2                                                                                                                                        | Harvard uses separate memory/bus/address space // von Neumann uses combined memory/bus/address space; for instructions/program and data;  NE. Places, locations, registers, areas of memory A. Main memory NOTE: It must be clear that instructions/data are stored in separate memory, not separately in memory.  2 Mark is for AO1 (knowledge) Harvard; |

| Level o                                                                                | f response question                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Level                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Mark<br>Range |

| 3                                                                                      | At least five of the steps of the cycle have been correctly identified in order/the steps are all in correct order and covering all three of the stages (fetch, decode, execute). For the top mark in this level thorough understanding of how the cycle works is evident.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-6           |

| 2                                                                                      | At least three steps of the cycle have been identified in order, covering at least two of the stages (fetch, decode, execute). Some understanding of how the cycle works is evident.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-4           |

| 1                                                                                      | At least one step of the cycle have been identified, covering at least one stage (fetch, decode or execute). The order of the steps may not be correct. Little understanding of how the cycle works is evident.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-2           |

| Points                                                                                 | may include:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| MAR Address Transfer Content MBR Increme after tra Increme Content  Decode The content | is of Program Counter / PC transferred to Memory Address Register is bus used to transfer this address to main memory in of content uses the data bus its of addressed memory location loaded into the Memory Buffer Region int (contents of) Program Counter / PC A. at any part of fetch processing PC to MAR interior PC and fetch simultaneously its of MBR copied to CIR instruction held by the (Current) Instruction Register / (C)IR introl unit decodes the instruction ion split into opcode and operand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | gister /      |

| If neces The ope process Result ( The ope Status r                                     | ssary, data is fetched ssary, data is stored in memory code identifies the type of operation/instruction to be performed (by the state of the state |               |

| NE. Reg                                                                                | gister notation<br>nory Data Register/MDR for Memory Buffer Register/MBR<br>rect headings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

### June 2017 Paper 2

#### 01 All marks AO1 (understanding) 2 Instruction and data can be accessed simultaneously; Avoid/reduce bottleneck of single data/address bus(es) // avoid/reduce delays waiting for memory fetches; Avoids possibility of data being executed as code (which is one method that can be exploited by hackers); Being able to use exclusively ROM for instruction memory prevents the program being modified/hacked; A. Program cannot be accidentally overwritten (by data) Instruction and data memory can have different word lengths; Different technologies can be used to implement instruction and data memory; Different quantities of instruction and data memory means that address lengths can differ between the two // memory address structures can differ; MAX 2 NE. So programs/tasks will run faster NE. More efficient

#### June 2009 Comp 2

| Internal Components<br>Data Bus | 10                                              | Peripherals<br>Keyboard | 2  |  |

|---------------------------------|-------------------------------------------------|-------------------------|----|--|

| Address Bus                     | 9                                               | Visual Display Unit     | 3  |  |

| Control Bus                     | NA                                              | Secondary Storage       | NA |  |

| VDU Controller                  | 8                                               |                         |    |  |

| Disk Controller                 | NA                                              |                         |    |  |

| Keyboard Controller             | 7                                               |                         |    |  |

| Main Memory                     | 5                                               |                         |    |  |

| Processor                       | 4                                               |                         |    |  |

|                                 | oair (8,3)<br>oair (7,2)<br>IF ANSW<br>ABLES. A | VERS WRITTEN ON IT      |    |  |

| OVERRIDE ANSW                   | EKS ON                                          | DIAGRAM.                |    |  |

## Specimen Paper 2

| 1 | All marks AO1 (understanding)                                     | 4 |

|---|-------------------------------------------------------------------|---|

|   | Correct Name from List                                            | - |

|   | B Visual display unit;                                            |   |

|   | C Processor;                                                      |   |

|   | D Main memory;                                                    |   |

|   | E Keyboard;                                                       |   |

|   | 1 mark per correct answer A. If same response used more than once |   |