# AQA Computer Science A-Level 4.6.4 Logic gates

**Past Paper Questions**

# January 2009 Comp 2

10 (a) Complete the truth tables for the following logic gates.

OR gate

| Input<br>A | Input<br>B | Output |

|------------|------------|--------|

| 0          | 0          |        |

| 0          | 1          |        |

| 1          | 0          |        |

| 1          | 1          |        |

AND gate

| Input<br>A | Input<br>B | Output |

|------------|------------|--------|

| 0          | 0          |        |

| 0          | 1          |        |

| 1          | 0          |        |

| 1          | 1          |        |

(2 marks)

| 10 (b | (b) | (i) | A single output Q is produced from three inputs A, B and C. Output Q is required to be 1 only if inputs A and B are 1, or input C is 1 and input B is 0. |

|-------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |     |     | Express this as a Boolean equation.                                                                                                                      |

|       |     |     | Q =                                                                                                                                                      |

|       |     |     | (2 marks)                                                                                                                                                |

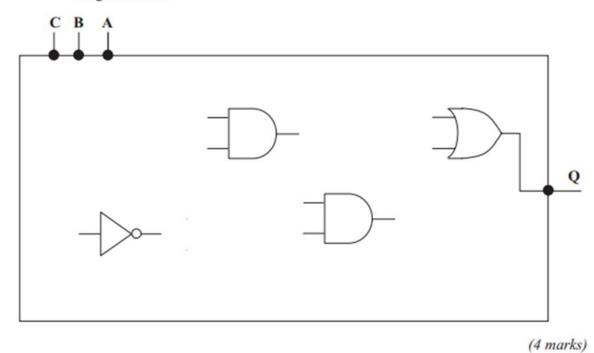

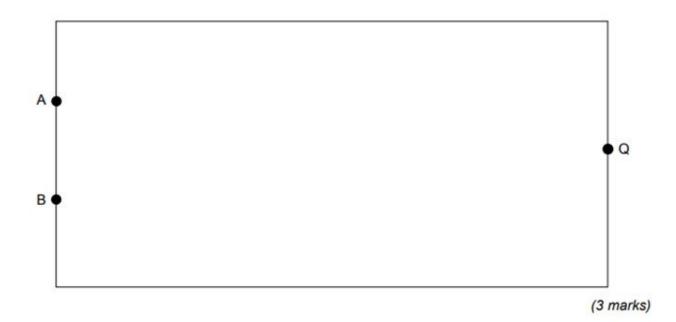

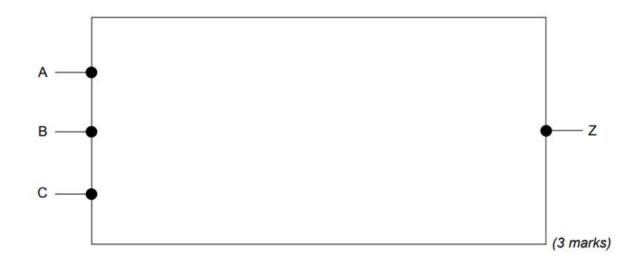

10 (b) (ii) Represent this Boolean equation diagrammatically by completing the logic gate diagram below.

# January 2010 Comp 2

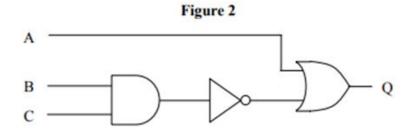

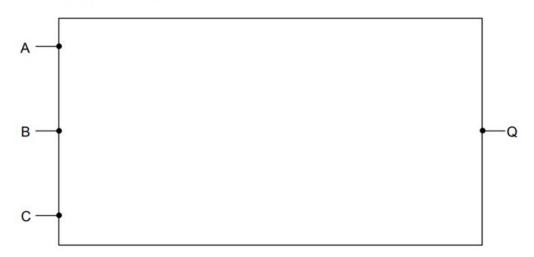

7 Figure 2 shows a logic circuit.

7 (a) Complete the truth table below for the logic circuit shown in Figure 2. Write the correct value of the output Q for each of the listed sets of inputs.

| Input<br>A | Input<br>B | Input<br>C | Output<br>Q |

|------------|------------|------------|-------------|

| 1          | 0          | 1          |             |

| 0          | 1          | 0          |             |

| 0          | 1          | 1          |             |

(3 marks)

| 7 | (b) | Two   | of the gates in the circuit shown in Figure 2 could be replaced by   | y a single gate. |

|---|-----|-------|----------------------------------------------------------------------|------------------|

| 7 | (b) | (i)   | Which two gates could be replaced?                                   |                  |

|   |     |       | ***************************************                              | (1 mark)         |

| 7 | (b) | (ii)  | What single gate would be used instead?                              |                  |

|   |     |       |                                                                      | (1 mark)         |

| 7 | (c) | Why   | is it an advantage to use as few gates as possible in a logic circui | it?              |

|   |     | ••••• |                                                                      |                  |

|   |     |       |                                                                      | (1 mark)         |

# January 2011 Comp 2

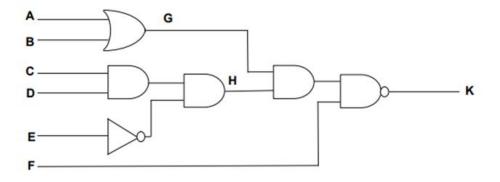

#### 2 Figure 2 shows a logic circuit.

Figure 2

Complete the truth table for the inputs that have been given.

| Inputs |   |   |   |   |   |   |   |   |

|--------|---|---|---|---|---|---|---|---|

| Α      | В | С | D | E | F | G | Н | K |

| 0      | 0 | 1 | 1 | 0 | 0 |   |   |   |

| 0      | 1 | 1 | 1 | 0 | 1 |   |   |   |

| 1      | 0 | 1 | 1 | 1 | 0 |   |   |   |

| 1      | 1 | 1 | 1 | 1 | 1 |   |   |   |

(3 marks)

# January 2012 Comp 2

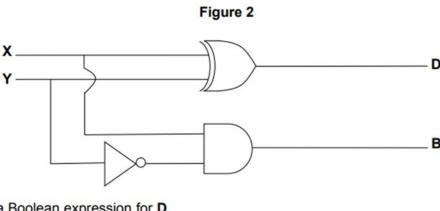

2 Figure 2 below shows a logic circuit.

|       |                                           | В       |

|-------|-------------------------------------------|---------|

| 2 (a) | Write a Boolean expression for <b>D</b> . |         |

|       |                                           | (1 mark |

| 2 (b) | Write a Boolean expression for <b>B</b> . |         |

|       |                                           | (1 mark |

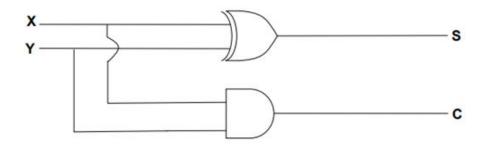

2 (c) Figure 3 below shows a different logic circuit.

Figure 3

2 (c) (i) Complete the truth table below for the logic circuit in Figure 3.

| Inputs |   | Out | uts |

|--------|---|-----|-----|

| X      | Y | С   | S   |

| 0      | 0 |     |     |

| 0      | 1 |     |     |

| 1      | 0 |     |     |

| 1      | 1 |     |     |

(2 marks)

| 2 (c) (ii) | What arithmetic function does the logic circuit in Figure 3 perform? |   |  |  |  |

|------------|----------------------------------------------------------------------|---|--|--|--|

|            | (1 mai                                                               | k |  |  |  |

# January 2013 Comp 2

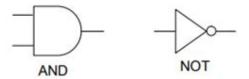

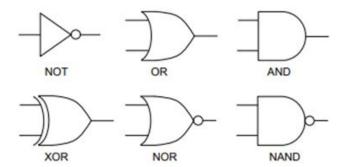

4 (a) Represent the Boolean equation  $Q = \overline{\overline{A} \cdot \overline{B}}$  as a logic circuit by drawing a diagram in the space below using **only** the following symbols:

**4 (b)** Use the following truth tables to demonstrate that  $A + B = \overline{A} \cdot \overline{B}$

| A | В | A+B |

|---|---|-----|

| 0 | 0 |     |

| 0 | 1 |     |

| 1 | 0 |     |

| 1 | 1 |     |

| A | В | Ā | B | Ā.B | A.B |

|---|---|---|---|-----|-----|

| 0 | 0 |   |   |     |     |

| 0 | 1 |   |   |     |     |

| 1 | 0 |   |   |     |     |

| 1 | 1 |   |   |     |     |

(4 marks)

### June 2010 Comp 2

9 (a) Complete the truth tables for the following logic gates.

| li li      | OR Gate    |             |  |  |  |  |  |

|------------|------------|-------------|--|--|--|--|--|

| Input<br>A | Input<br>B | Output<br>Q |  |  |  |  |  |

| 0          | 0          |             |  |  |  |  |  |

| 0          | 1          |             |  |  |  |  |  |

| 1          | 0          |             |  |  |  |  |  |

| 1          | 1          |             |  |  |  |  |  |

| XOR Gate   |            |             |  |  |

|------------|------------|-------------|--|--|

| Input<br>A | Input<br>B | Output<br>Q |  |  |

| 0          | 0          |             |  |  |

| 0          | 0 1        |             |  |  |

| 1          | 0          |             |  |  |

| 1          | 1          |             |  |  |

(2 marks)

9 (b) Represent the Boolean equation  $Q = A + B \cdot \overline{C}$  as a logic circuit by drawing a diagram of it in the space below.

(3 marks)

# June 2011 Comp 2

3 (a) Complete the truth tables for the following logic gates.

| NAND Gate  |            |        |  |  |

|------------|------------|--------|--|--|

| Input<br>X | Input<br>Y | Output |  |  |

| 0          | 0          |        |  |  |

| 0          | 1          |        |  |  |

| 1          | 0          |        |  |  |

| 1          | 1          |        |  |  |

| NOR Gate   |            |        |  |  |

|------------|------------|--------|--|--|

| Input<br>X | Input<br>Y | Output |  |  |

| 0          | 0          |        |  |  |

| 0          | 1          |        |  |  |

| 1          | 0          |        |  |  |

| 1          | 1          |        |  |  |

(2 marks)

3 (b) Represent the Boolean equation  $Z = \overline{A} \cdot \overline{B} + C$  in the form of a logic circuit by drawing a diagram in the space below using the following symbols.

#### June 2012 Comp 2

8 (a) Complete the truth tables for the following logic gates.

| AND Gate |          |  |  |  |  |

|----------|----------|--|--|--|--|

| Input X  | Output Q |  |  |  |  |

| 0        | 0        |  |  |  |  |

| 0        | 1        |  |  |  |  |

| 1        | 0        |  |  |  |  |

| 1        | 1        |  |  |  |  |

| XOR Gate |          |  |  |  |

|----------|----------|--|--|--|

| Input X  | Output Q |  |  |  |

| 0        | 0        |  |  |  |

| 0        | 1        |  |  |  |

| 1        | 0        |  |  |  |

| 1        | 1        |  |  |  |

(2 marks)

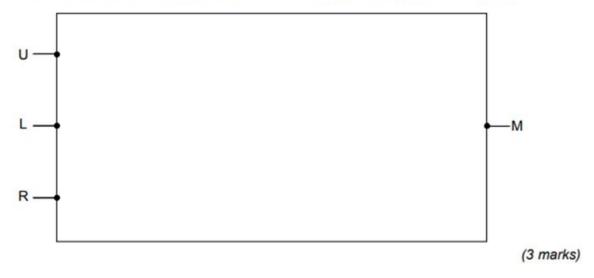

- **8 (b)** A line-following robot has three sensors. It moves along a black line on a white background whilst the following conditions are met:

- the ultrasonic sensor U does not detect any obstacle

- either, but not both, of the infrared sensors L and R are on the black line.

Sensor U returns 1 if it detects an obstacle and 0 if the path is clear.

Sensors L and R each return 1 if they detect black and 0 if they detect white.

A logic circuit will process the input from the sensors and produce an output M.

M should be 1 if the robot is to move and 0 if the robot should stop.

8 (b) (i) Represent the output M as a Boolean expression.

| M = |          |

|-----|----------|

|     | (3 marks |

#### 8 (b) (ii) The following symbols are used to represent logic gates:

Using a combination of any of the above logic gates draw a logic circuit for this system in the box below. You will **not** need to use all of the different types of logic gates.

# June 2013 Comp 2

6 (a) State the names of the logic gates represented by each of the three truth tables below.

| Input A | Input B | Output |  |  |

|---------|---------|--------|--|--|

| 0       | 0       | 0      |  |  |

| 0       | 1       | 0      |  |  |

| 1       | 0       | 0      |  |  |

| 1       | 1       | 1      |  |  |

Logic gate name .....

| Input A | Input B | Output |

|---------|---------|--------|

| 0       | 0       | 1      |

| 0       | 1       | 0      |

| 1       | 0       | 0      |

| 1       | 1       | 0      |

Logic gate name .....

| Input A | Input B | Output |

|---------|---------|--------|

| 0       | 0       | 0      |

| 0       | 1       | 1      |

| 1       | 0       | 1      |

| 1       | 1       | 0      |

Logic gate name .....

(3 marks)

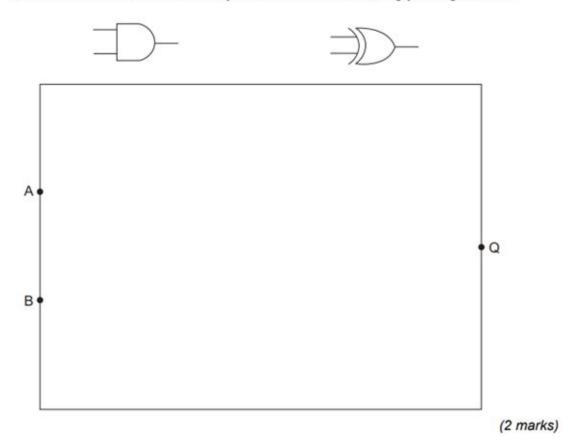

6 (c) Draw a logic circuit for the following Boolean expression:

$$Q = (A \oplus B) \cdot B$$

You will need to make use of the symbols below when drawing your logic circuit.

# June 2016 AS Paper 2

0 5

0 5 . 1 What is the name of the logic gate represented by the truth table and symbol shown in **Figure 5**?

[1 mark]

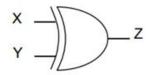

Figure 5

| X | Y   | Z |  |  |

|---|-----|---|--|--|

| 0 | 0   | 0 |  |  |

| 0 | 1   | 1 |  |  |

| 1 | 0 1 |   |  |  |

| 1 | 1   | 0 |  |  |

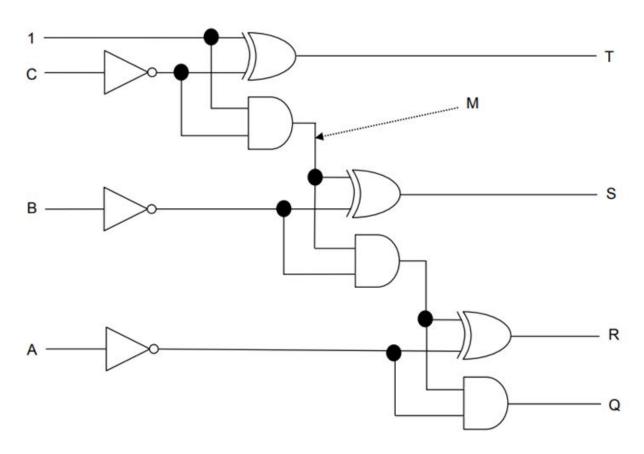

Figure 6 shows a logic circuit that might be found inside a processor.

#### Figure 6

0 5 . 2 The value at **M** (indicated by the arrow in **Figure 6**) is represented by the following Boolean expression.

1.C

Simplify this Boolean expression.

[1 mark]

| 0 5 . 3 | The output <b>T</b> (in                             | Figure   |          | oresente<br>⊕ Ĉ | ed by the | followin | g Boolean    | expression. |

|---------|-----------------------------------------------------|----------|----------|-----------------|-----------|----------|--------------|-------------|

|         | Simplify this Boo                                   | olean ex | pression | 1.              |           |          |              | [1 mark     |

| 0 5 . 4 | Complete the m                                      |          |          |                 | n table f | or the c | ircuit in Fi | [3 marks    |

|         |                                                     |          | Inputs   |                 | 1)        | Outputs  | 5            |             |

|         |                                                     | С        | В        | Α               | Т         | S        | R            |             |

|         |                                                     | 0        | 0        | 0               | 0         | 0        | 0            |             |

|         |                                                     | 0        | 0        | 1               |           |          |              |             |

|         |                                                     | 0        | 1        | 0               |           |          |              |             |

|         | 3                                                   | 0        | 1        | 1               | 0         | 1        | 0            |             |

| 0 5 . 5 | The logic circuit 3-bit binary num when subtracting | ber. Ex  | plain ho | w this ci       | rcuit cou | ld be us |              |             |

# June 2017 AS Paper 2

0 5

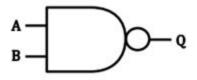

Figure 4

| A | В | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

0 5. 1 What is the name of the logic gate represented by the truth table and symbol shown in Figure 4?

[1 mark]

0 5 . 2 Complete the truth table below to prove that  $A + \overline{B}$  is equivalent to  $\overline{A} \cdot B$  [3 marks]

| A | В |  |  |  |

|---|---|--|--|--|

| 0 | 0 |  |  |  |

| 0 | 1 |  |  |  |

| 1 | 0 |  |  |  |

| 1 | 1 |  |  |  |

#### June 2017 Paper 2

| 0 | 4 |

|---|---|

|---|---|

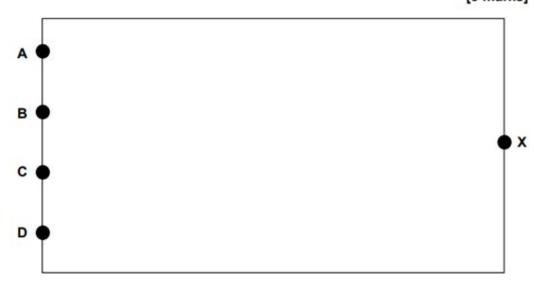

A computer process, X, can only start executing once processes A and B have finished executing and either communication channel C or communication channel D or both are available to use.

The states of processes and communication channels can be read using the following Boolean variables:

- A is set to TRUE if process A has completed and FALSE if process A is still running.

- B is set to TRUE if process B has completed and FALSE if process B is still running.

- C is set to TRUE if communication channel C is available and FALSE if it is not available.

- D is set to TRUE if communication channel D is available and FALSE if it is not available.

The Boolean variable **X** should be set to TRUE if the values of the variables **A**, **B**, **C** and **D** indicate that process X can start and to FALSE if they indicate that process X cannot start yet.

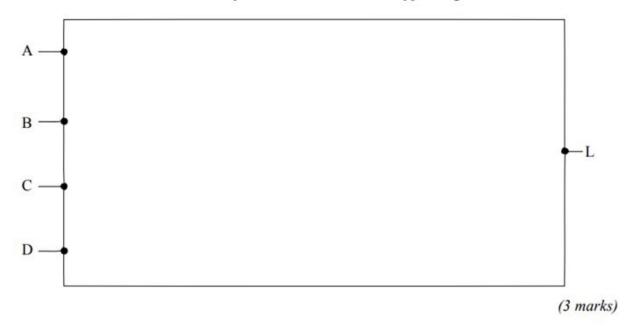

0 4 . 1

In the space below, draw a logic circuit that will represent the logic of the system described above for the inputs **A**, **B**, **C** and **D** and the output **X**.

[3 marks]

0 4 . 2

Write a Boolean expression to represent the logic used to start process X.

[2 marks]

X =

| 0 4 . 4      | D-type flip-fle Explain the                                                                                                                |        |                                               | 7 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |   | [1 mark] |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------|-----------------------------------------|---|----------|

|              |                                                                                                                                            |        |                                               |                                         |   |          |

| 0 4 . 5      | One input to a D-type flip-flop is a data signal.  State what the other input to a D-type flip-flop is and what it is used for.  [2 marks] |        |                                               |                                         |   |          |

|              |                                                                                                                                            |        |                                               |                                         |   | 30       |

|              |                                                                                                                                            |        |                                               |                                         |   |          |

| 4 (a) Look ( | at the truth tab                                                                                                                           |        | 2009 C                                        | Comp 2                                  |   |          |

| 4 (a) Look a | it the truth tat                                                                                                                           | Input  | Input                                         | Output                                  | 7 |          |

|              |                                                                                                                                            | A      | В                                             | Q                                       |   |          |

|              |                                                                                                                                            | 0      | 0                                             | 1                                       |   |          |

|              |                                                                                                                                            | 0      | 1                                             | 0                                       | - |          |

|              |                                                                                                                                            | 1      | 0                                             | 0                                       | _ |          |

| What I       | ogic gate doe                                                                                                                              | 100 mg | 1/2 N. M. | •                                       | J |          |

| ••••         | ••••••                                                                                                                                     | •••••• | •••••                                         |                                         |   | (1 mark) |

4 (b) An interior light in a two-door car is controlled by two switches that the driver can turn on or off and two sensors, one per door.

The switches are named A and B.

The door sensors are named C and D.

The interior light is named L.

If a door is open the output of its sensor is on.

If a door is closed the output of its sensor is off.

- If both switches A and B are off then the light L is always off.

- If switch A is on the light L is always on.

- If switch B is on and switch A is off then:

- o the light L turns on if one or more of the car doors is opened

- o the light L turns off if both of the doors are closed.

The following symbols are used to represent logic gates:

4 (b) (i) Using only AND, OR and NOT gates draw a logic circuit for this system in the box below. You may not need to use all three types of gate.

4 (b) (ii) Write a Boolean expression to represent the logic of the interior light system.

(1 mark)

# Specimen AS Paper 2

0 9 . 1 Complete **Table 5** and draw the symbol for an AND gate in the box.

[2 marks]

Table 5 - Truth table for an AND gate

| Input A | Input B | Output   |

|---------|---------|----------|

|         |         |          |

|         |         | <u> </u> |

|         |         |          |

| AND gate symbol |  |

|-----------------|--|

|                 |  |

|                 |  |

|                 |  |

## Specimen Paper 2

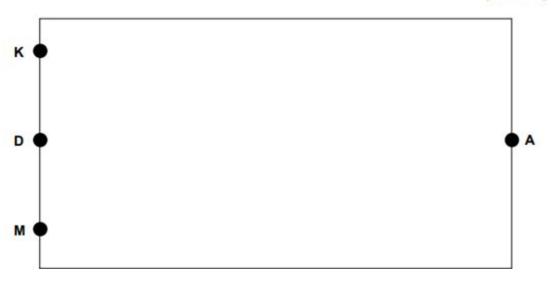

- 0 3 A burglar alarm system is to be implemented that has the following sensors:

- a door sensor D that outputs TRUE when the door is open and FALSE when the door is shut

- a pressure mat sensor M that outputs TRUE while a weight is detected on it and FALSE when no weight is detected on it.

The alarm also has a key **K** that turns the alarm on and off. **K** outputs a TRUE signal when the alarm is switched on and FALSE when the alarm is off.

The alarm output A sounds a bell. It should be TRUE if:

- · the alarm is on AND

- . either of the sensors D or M are set to the value TRUE.

- 0 3 . 1 In the space below, draw a logic circuit that will behave as described above for the inputs D, M and K and the output A.

[2 marks]

0 3 . 2 Write a Boolean expression to represent the logic of this alarm system.

[2 marks]

A =

| 0 3 . 3 | In this alarm system, the alarm bell will sound only while the door is open or a weight is placed on the pressure mat. If someone who has stepped on to the mat moves off it, or an open door is closed, the alarm bell will stop ringing.  A D-type flip-flop could be incorporated into the logic circuit so that the alarm bell would continue to sound after a person closed the door or moved off the pressure mat.  Explain how this could be achieved. In your answer refer to: |  |  |  |  |  |                                                                                                                                                                                                                           |  |  |  |  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  | <ul> <li>why a D-type flip-flop would be suitable for this task</li> <li>where the D-type flip-flop would need to be inserted into the circuit</li> <li>what additional input the D-type flip-flop would need.</li> </ul> |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  | [3 marks]                                                                                                                                                                                                                 |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |                                                                                                                                                                                                                           |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |                                                                                                                                                                                                                           |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |                                                                                                                                                                                                                           |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |                                                                                                                                                                                                                           |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |                                                                                                                                                                                                                           |  |  |  |  |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |                                                                                                                                                                                                                           |  |  |  |  |