# AQA Computer Science A-Level 4.6.4 Logic gates Intermediate Notes

# **Specification:**

# 4.6.4.1 Logic gates:

Construct truth tables for the following logic gates:

- NOT

- AND

- OR

- XOR

- NAND

- NOR

Be familiar with drawing and interpreting logic gate circuit diagrams involving one or more of the above gates.

Complete a truth table for a given logic gate circuit.

Write a Boolean expression for a given logic gate circuit.

Draw an equivalent logic gate circuit for a given Boolean expression.

Recognise and trace the logic of the circuits of a half-adder and a full-adder.

Construct the circuit for a half-adder.

Be familiar with the use of the edge-triggered D-type flip-flop as a memory unit.

# Logic Gates

Logic gates are devices which apply logical operations to one or more Boolean (TRUE or FALSE) inputs in order to produce a single Boolean output.

Within a computer's processor, logic gates are combined to form logic circuits which can perform more complex operations.

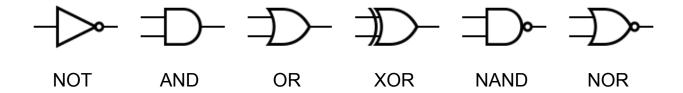

# **Logic Gate Symbols**

Each of the six required logic gates has a symbol which you should learn. The symbols have inputs on the left and outputs on the right.

## **Truth Tables**

A truth table shows every possible combination of inputs and the corresponding output for a logic gate or logic circuit. The inputs are labelled alphabetically starting with A and the output is usually labelled Q.

### **NOT**

The NOT gate has one input and one output. The gate's output is always the opposite of its input. For example, if the input to the gate is a 1, it will output 0.

| Α | Q |

|---|---|

| 0 | 1 |

| 1 | 0 |

The truth table for the NOT gate has just two columns, the input A and the output Q. There are just two possible inputs, 1 and 0.

# Note

In Boolean logic, an overline signifies that the value(s) below have the NOT operation applied to

## <u>AND</u>

The AND gate has two inputs, labelled A and B in the truth table below, and outputs the two inputs multiplied together.

| Α | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

$$Q = A \times B$$

The AND gate only outputs TRUE (1) when both inputs are TRUE, otherwise it outputs FALSE.

### <u>OR</u>

In the same way that AND multiplies its inputs, OR adds them together.

| Α | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

$$Q = A + B$$

OR only outputs FALSE when both inputs are FALSE. When one or more of the gate's inputs are TRUE, the logic gate outputs TRUE.

### **XOR**

The XOR gate's full name is exclusively or and it outputs TRUE when exactly one of its inputs is TRUE. The gate's truth table is the same as the OR gate with the exception of the last line in which FALSE is output with two TRUE inputs.

| Α | В | Q |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

# Synoptic Link

The **XOR** operation is used in the **Vernam cipher**.

The Vernam cipher is covered in more detail in representing images, sound and other data under fundamentals of data representation.

$$Q = A XOR B$$

### **NAND**

NAND is short for NOT AND. The NAND gate is actually a combination of two gates which we've already covered, the NOT gate and the AND gate.

The NAND gate's truth table is the same as the AND gate's truth table, but the output is reversed.

| Α | В | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

$$Q = \overline{A \times B}$$

# <u>NOR</u>

NOR, short for NOT OR is a combination of the two logic gates NOT and OR.

Therefore, the NOR gate's truth table is the same as the OR gate's table, just with the output reversed.

| Α | В | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

$$Q = \overline{A + B}$$

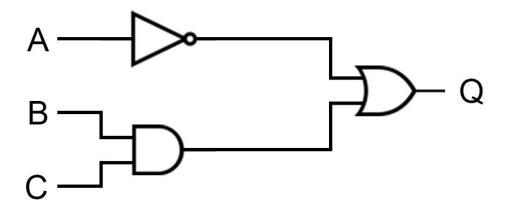

# **Combining Logic Gates**

Logic gates can be combined to form more complex circuits. You may be asked to draw or interpret a logic circuit involving multiple logic gates.

The logic circuit above combines three logic gates and can be represented using the logical expression below.

# There are me

There are more examples of logical expressions in the notes for Boolean algebra.

Synoptic Link

$$Q = (B \times C) + \overline{A}$$

In order to create a truth table for this circuit, we first need to fill in all the possible permutations of inputs like so:

| A | В | С |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 0 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

| 1 | 1 | 1 |

Next, we add columns for each of the elements that make up the logical expression such as  $B \times C$  and  $\overline{A}$ . This will make it easier for us to combine them to form the final expression.

| A | В | C | $B \times C$ | Ā | $(B \times C) + \overline{A}$ |

|---|---|---|--------------|---|-------------------------------|

| 0 | 0 | 0 | 0            | 1 | 1                             |

| 0 | 0 | 1 | 0            | 1 | 1                             |

| 0 | 1 | 0 | 0            | 1 | 1                             |

| 0 | 1 | 1 | 1            | 1 | 1                             |

| 1 | 0 | 0 | 0            | 0 | 0                             |

| 1 | 0 | 1 | 0            | 0 | 0                             |

| 1 | 1 | 0 | 0            | 0 | 0                             |

| 1 | 1 | 1 | 1            | 0 | 1                             |

Once the column in the truth table for the finished expression is complete, the columns used for working can be removed and the final column renamed Q.

| A | В | C | Q |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

### **Adders**

An adder is a logic circuit that can be used to add Boolean values together. There are two types of adder that you need to be aware of: half adders and full adders.

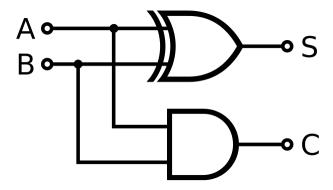

### Half adders

A half adder is a logic circuit two inputs, two outputs and two logic gates. The circuit can be used to add two Boolean values.

The two inputs are labelled A and B and the outputs are labelled S and C. Short for sum and carry.

| Α | В | S | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

$$0 + 0 = 0$$

$$0 + 1 = 1$$

$$1 + 0 = 1$$

$$1 + 1 = 0$$

carry 1

You need to be able to draw the logic circuit for a half adder.

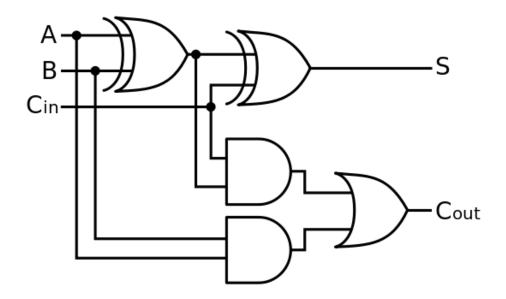

# Full adders

A full adder has three inputs and two outputs.

The three inputs are labelled A, B and  $C_{in}$  for carry in. The two outputs are labelled S for sum and  $C_{out}$  for carry out.

You need to be able to recognise this circuit as a full adder, but you're not expected to be able to draw it.

The full adder's truth table looks like this:

| A | В | C <sub>in</sub> | S | C <sub>out</sub> |

|---|---|-----------------|---|------------------|

| 0 | 0 | 0               | 0 | 0                |

| 0 | 0 | 1               | 1 | 0                |

| 0 | 1 | 0               | 1 | 0                |

| 0 | 1 | 1               | 0 | 1                |

| 1 | 0 | 0               | 1 | 0                |

| 1 | 0 | 1               | 0 | 1                |

| 1 | 1 | 0               | 0 | 1                |

| 1 | 1 | 1               | 1 | 1                |

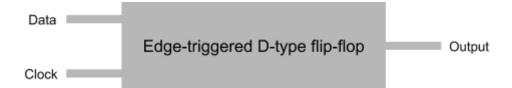

# **Edge-triggered D-type flip-flop**

An edge-triggered D-type flip-flop is a logic circuit which can be used as a memory unit for storing the value of a single bit.

An edge-triggered D-type flip-flop has two inputs, one for data and another for a clock signal. There is one output, which always holds the value of the stored bit.